普林斯頓、英特爾提出ParNet,速度和準確性顯著優于ResNet

深度是深度神經網絡的關鍵,但更多的深度意味著更多的序列計算和更多的延遲。這就引出了一個問題——是否有可能構建高性能的「非深度」神經網絡?

近日,普林斯頓大學和英特爾實驗室的一項研究證明了這一觀點的可行性。該研究使用并行子網絡而不是一層又一層地堆疊,這有助于在保持高性能的同時有效地減少深度。

論文地址:https://arxiv.org/abs/2110.07641

通過利用并行子結構,該研究首次表明深度僅為 12 的網絡可在 ImageNet 上實現超過 80%、在 CIFAR10 上實現超過 96%、在 CIFAR100 上實現 81% 的 top-1 準確率。該研究還表明,具有低深度主干網絡的模型可以在 MS-COCO 上達到 48% 的 AP 指標。研究者分析了該設計的擴展規則,并展示了如何在不改變網絡深度的情況下提高性能。最后,研究者提供了關于如何使用非深度網絡來構建低延遲識別系統的概念證明。

方法

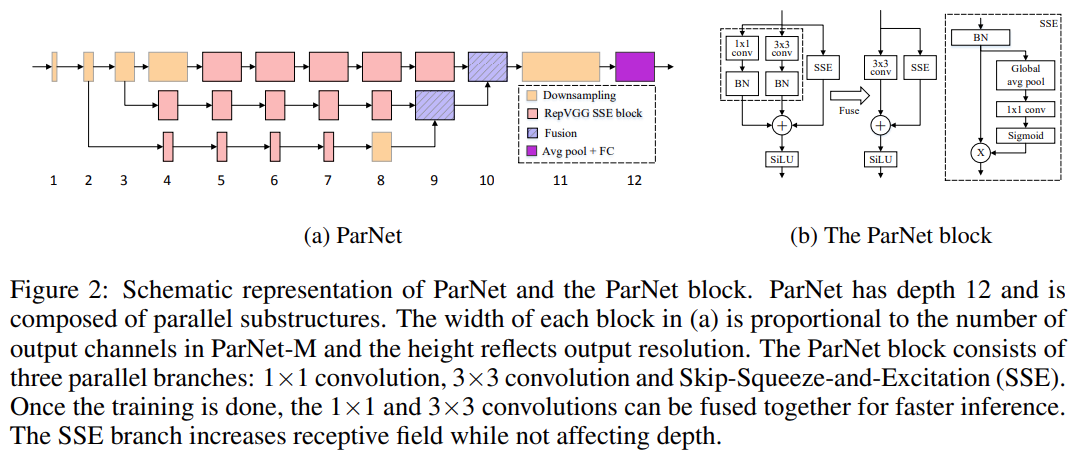

該研究提出了一種深度較低但仍能在多項基準上實現高性能的網絡架構 ParNet,ParNet 由處理不同分辨率特征的并行子結構組成。這些并行子結構稱為流(stream),來自不同流的特征在網絡的后期融合,融合的特征用于下游任務。圖 2a 提供了 ParNet 的示意圖。

圖 2

ParNet Block

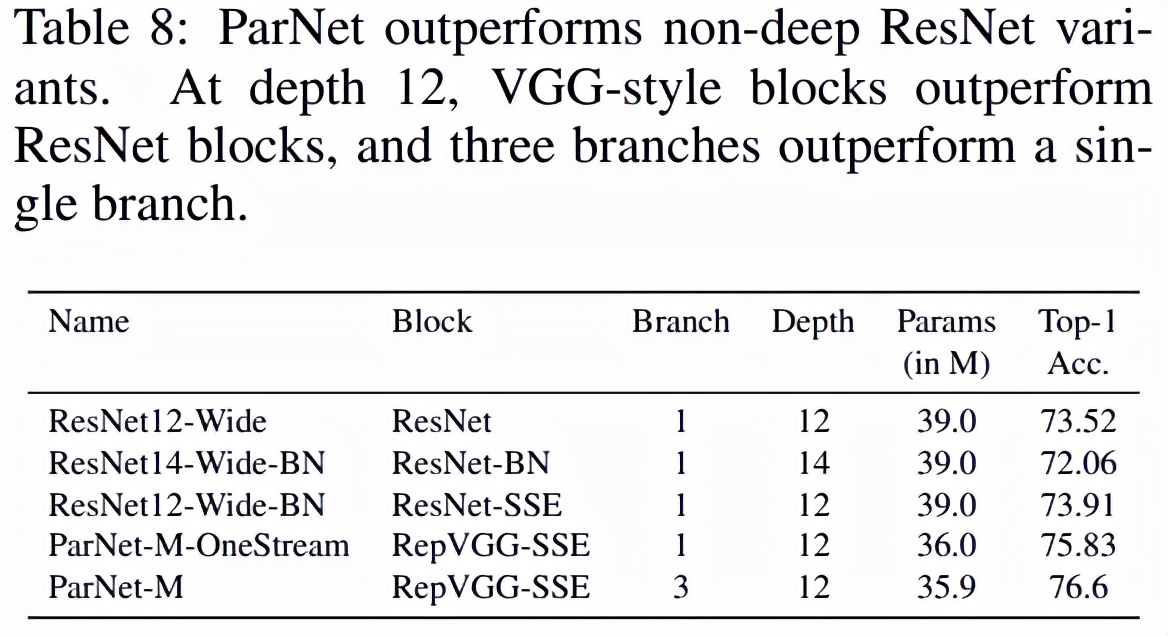

ParNet 中使用了 VGG 風格的 block(Simonyan & Zisserman,2015)。為了探究非深度網絡是否可以實現高性能,該研究通過實驗發現 VGG 風格 block 比 ResNet 風格 block 更合適(如下表 8 所示)。一般來說,訓練 VGG 風格的網絡比 ResNet 更難(He 等,2016a)。但是最近的一些工作表明,使用「結構重參數化」方法(Ding 等,2021),會讓 VGG 風格 block 更容易訓練。

訓練期間,該研究在 3×3 卷積 block 上使用多個分支。訓練完成后,多個分支可以融合為一個 3×3 的卷積 block。因此,最終得到一個僅由 3×3 block 和非線性組成的簡單網絡。block 的這種重參數化或融合(fusion)有助于減少推理期間的延遲。

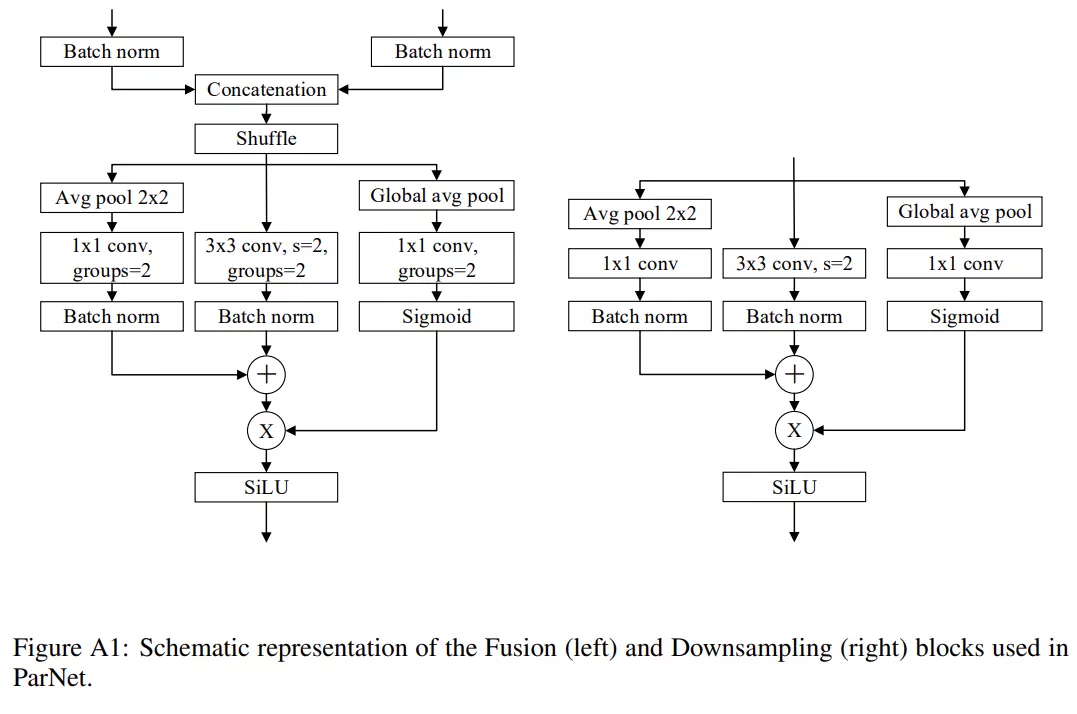

降采樣和融合 block

除了輸入和輸出大小相同的 RepVGG-SSE block 之外,ParNet 還包含降采樣(downsampling)和融合 block。降采樣 block 降低了分辨率并增加了寬度以實現多尺度(multi-scale)處理,而融合 block 將來自多個分辨率的信息組合。在降采樣 block 中,沒有殘差連接(skip connection);相反,該研究添加了一個與卷積層并行的單層 SE 模塊。

此外,該研究在 1×1 卷積分支中添加了 2D 平均池化。融合 block 和降采樣 block 類似,但還包含一個額外的串聯(concatenation)層。由于串聯,融合 block 的輸入通道數是降采樣 block 的兩倍。為了減少參數量,該研究的降采樣和融合 block 的設計如下圖所示。

網絡架構

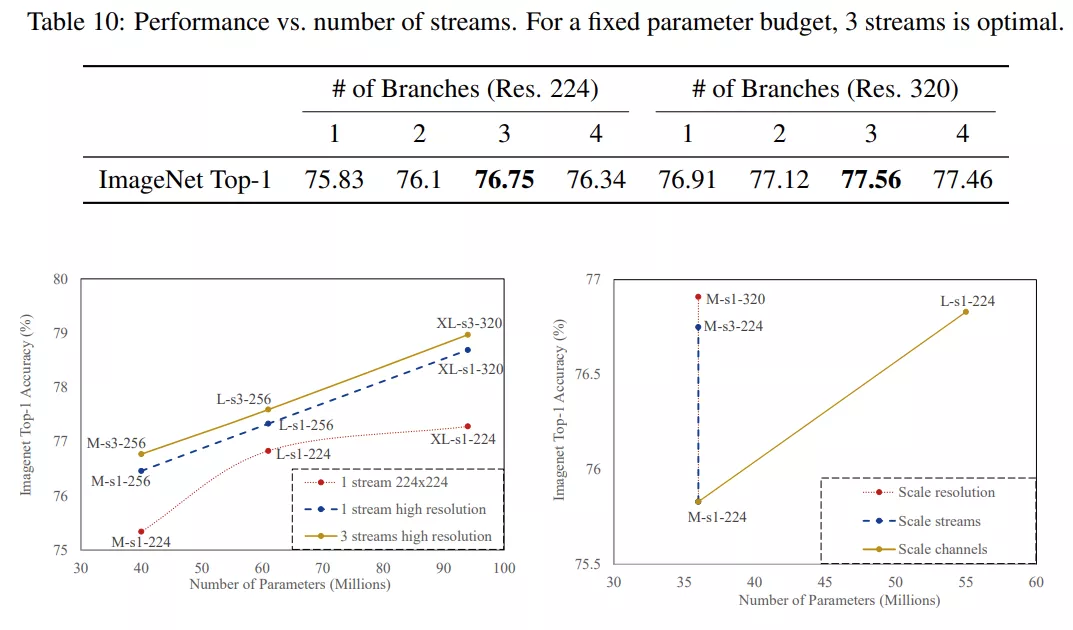

圖 2a 展示了用于 ImageNet 數據集的 ParNet 模型示意圖。初始層由一系列降采樣塊組成,降采樣 block 2、3 和 4 的輸出分別饋送到流 1、2 和 3。研究者發現 3 是給定參數預算的最佳流數(如表 10 所示)。每個流由一系列不同分辨率處理特征的 RepVGG-SSE block 組成。然后來自不同流的特征由融合 block 使用串聯進行融合。最后,輸出被傳遞到深度為 11 的降采樣 block。與 RepVGG(Ding 等, 2021)類似,該研究對最后一個降采樣層使用更大的寬度。

擴展 ParNet

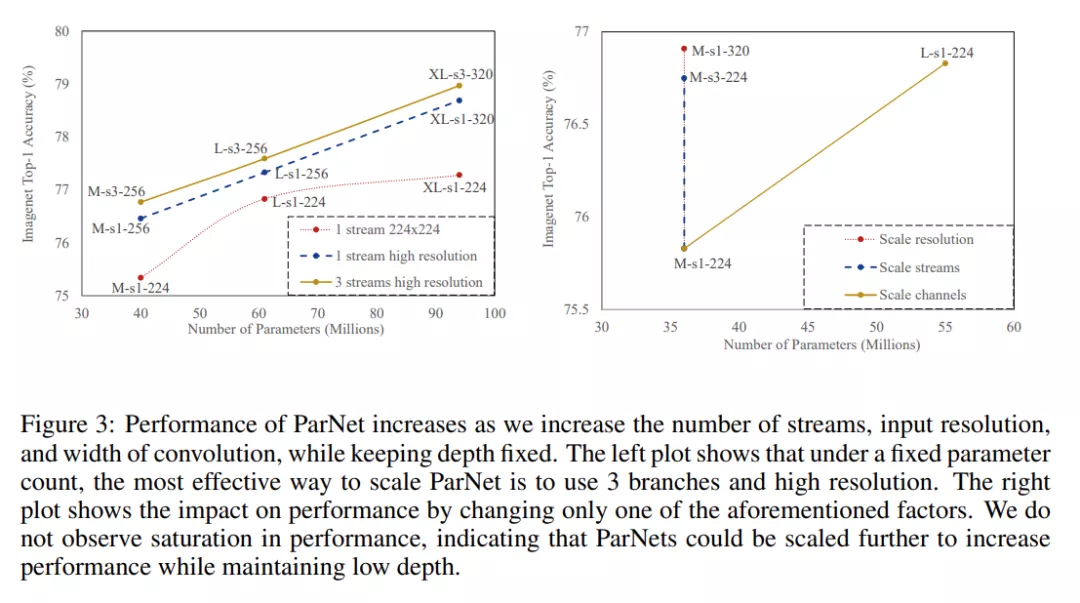

據觀察,神經網絡可以通過擴大網絡規模來獲得更高的準確度。之前的研究 (Tan & Le, 2019) 擴展了寬度、分辨率和深度。由于本研究的目標是評估是否可以在深度較低的情況下實現高性能,因此研究者將模型的深度保持不變,通過增加寬度、分辨率和流數來擴展 ParNet。

對于 CIFAR10 和 CIFAR100,該研究增加了網絡的寬度,同時將分辨率保持為 32,流數保持為 3。對于 ImageNet,該研究在三個不同的維度上進行了實驗,如下圖 3 所示。

并行架構的實際優勢

目前 5 納米光刻工藝已接近 0.5 納米晶硅尺寸,處理器頻率進一步提升的空間有限。這意味著神經網絡的更快推理必須依賴計算的并行化。單個單片 GPU 的性能增長也在放緩,預計傳統光刻可實現的最大芯片尺寸將達到 800 平方毫米(Arunkumar 等,2017)。總體而言,未來在處理器頻率、芯片尺寸以及每個處理器的晶體管數等方面都將維持一個平穩狀態。

為了解決這個問題,最近的一些工作提出了多芯片模塊 GPU (MCM-GPU),比最大的可實現單片 GPU 更快。用中型芯片取代大型芯片有望降低硅成本。這樣的芯片設計有利于具有并行分支的分區算法,算法之間交換有限的數據并且盡可能地分別獨立執行。基于這些因素,非深度并行結構將有利于實現快速推理,尤其是對于未來的硬件。

實驗結果

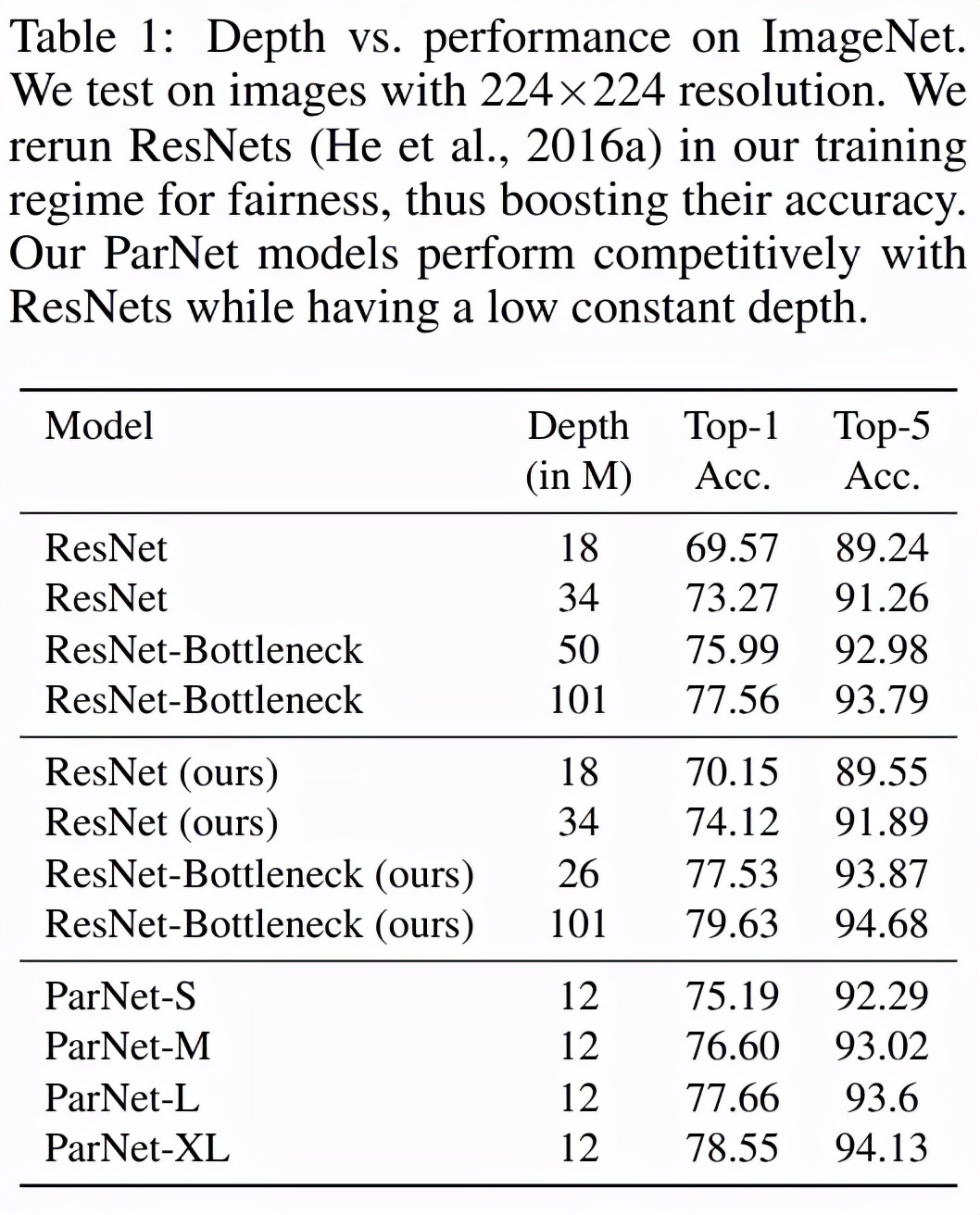

表 1 展示了 ParNet 在 ImageNet 上的性能。該研究發現,深度僅為 12 的網絡就可以實現驚人的高性能。為了與 ResNet 進行公平比較,研究者使用相同的訓練協議和數據增強重新訓練 ResNet,這將 ResNet 的性能提升到了超越官方結果的水平。值得注意的是,該研究發現 ParNet-S 在參數數量較少的情況下(19M vs 22M)在準確率上比 ResNet34 高出 1 個百分點以上。ParNet 還通過瓶頸設計實現了與 ResNet 相當的性能,同時深度減少到 1/4-1/8。

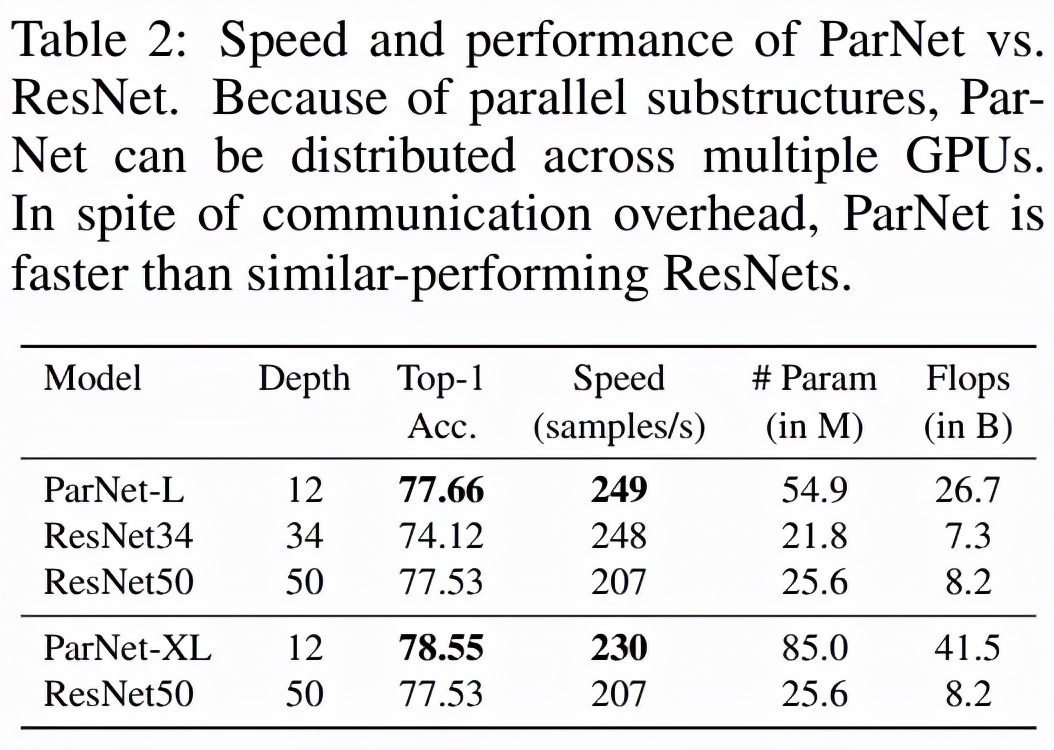

如下表 2 所示,ParNet 在準確率和速度上優于 ResNet,但參數和 flop 也更多。例如,ParNet-L 實現了比 ResNet34 和 ResNet50 更快的速度和更好的準確度。類似地,ParNet-XL 實現了比 ResNet50 更快的速度和更好的準確度,但具有更多的參數和 flop。這表明使用 ParNet 代替 ResNet 時存在速度與參數和 flop 之間的權衡。請注意,可以通過利用可以分布在 GPU 上的并行子結構來實現高速。

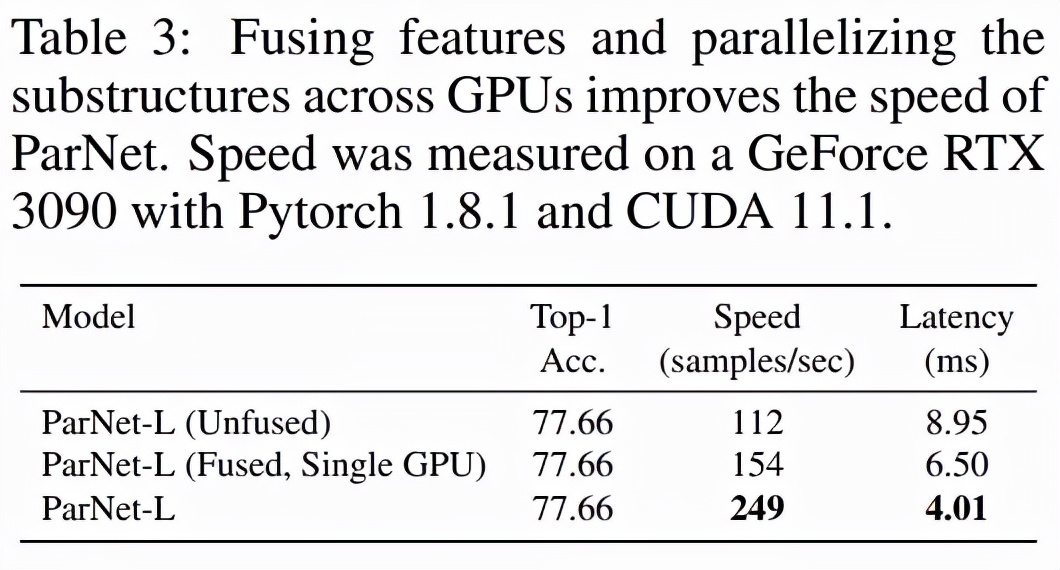

該研究測試了 ParNet 三種變體的速度:未融合、融合和多 GPU,結果如下表 3 所示。未融合的變體由 RepVGG-SSE 塊中的 3×3 和 1×1 分支組成。在融合變體中,使用結構重參數化技巧將 3×3 和 1×1 分支合并為一個 3×3 分支。對于融合和未融合變體,該研究使用單個 GPU 進行推理,而對于多 GPU 變體,使用了 3 個 GPU。對于多 GPU 變體,每個流都在單獨的 GPU 上啟動。當一個流中的所有層都被處理時,來自兩個相鄰流的結果將在其中一個 GPU 上連接并進一步處理。為了跨 GPU 傳輸數據,該研究使用了 PyTorch 中的 NCCL 后端。

該研究發現盡管存在通信開銷,但 ParNet 仍可以跨 GPU 有效并行化以進行快速推理。使用專門的硬件可以減少通信延遲,甚至可以實現更快的速度。

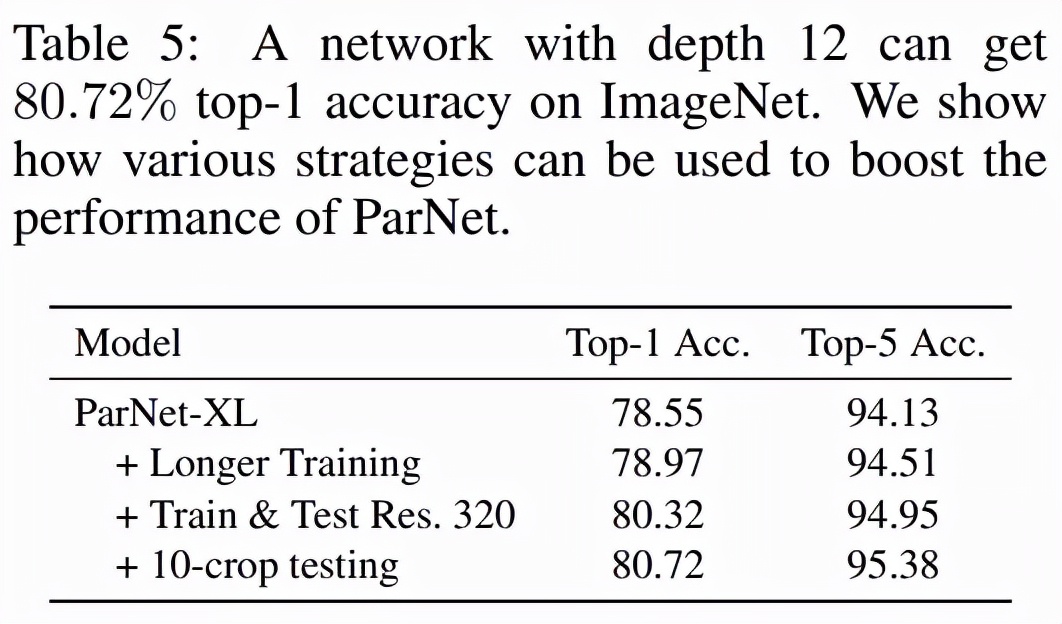

表 5 展示了提高 ParNet 性能的其他方法,例如使用更高分辨率的圖像、更長的訓練機制(200 個 epoch、余弦退火)和 10-crop 測試。這項研究有助于評估非深度模型在 ImageNet 等大規模數據集上可以實現的準確性。

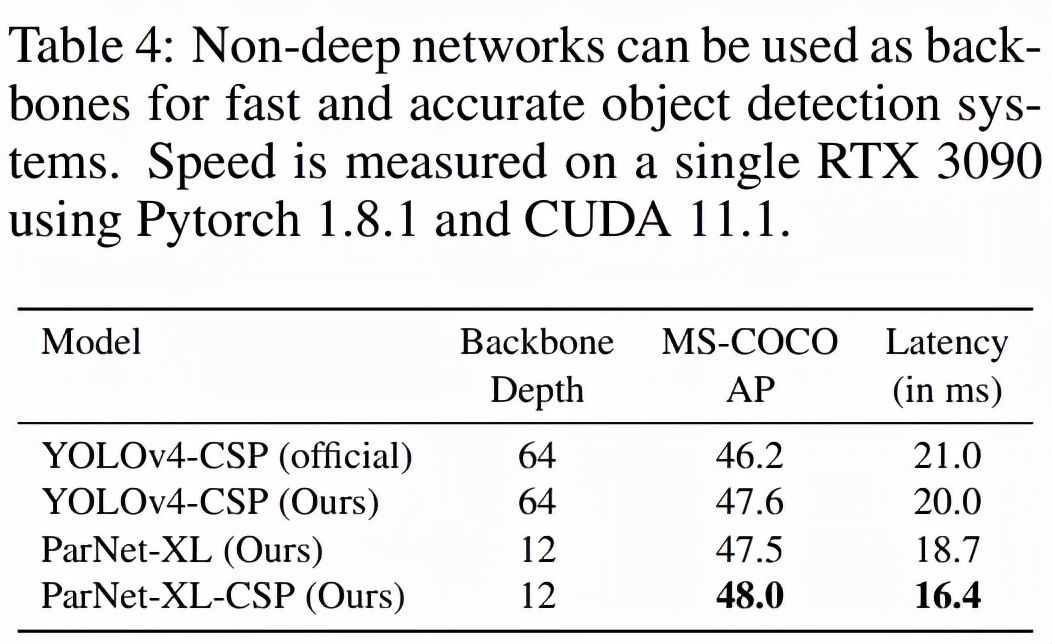

MS-COCO (Lin 等,2014) 是一個目標檢測數據集,其中包含具有常見對象的日常場景圖像。研究者用 COCO-2017 數據集進行了評估。如下表 4 所示,即使在單個 GPU 上,ParNet 也實現了比基線更高的速度。這闡明了如何使用非深度網絡來制作快速目標檢測系統。

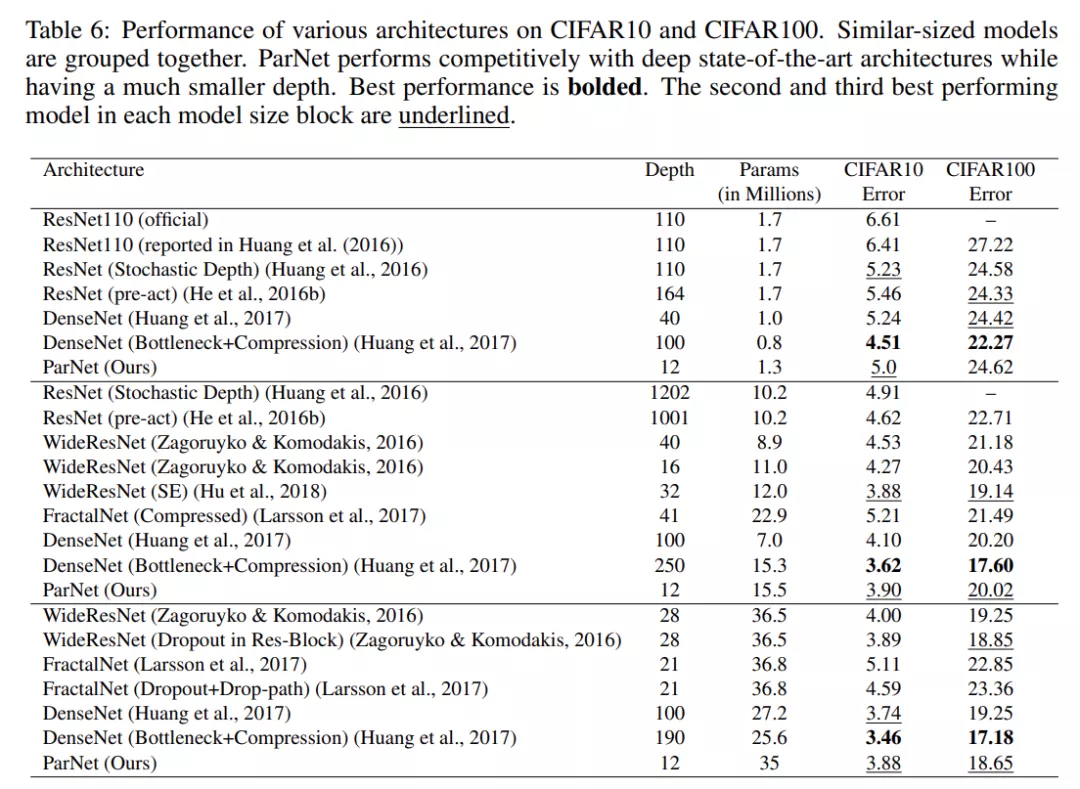

表 6 總結了各種網絡在 CIFAR10 和 CIFAR100 上的性能。

消融實驗

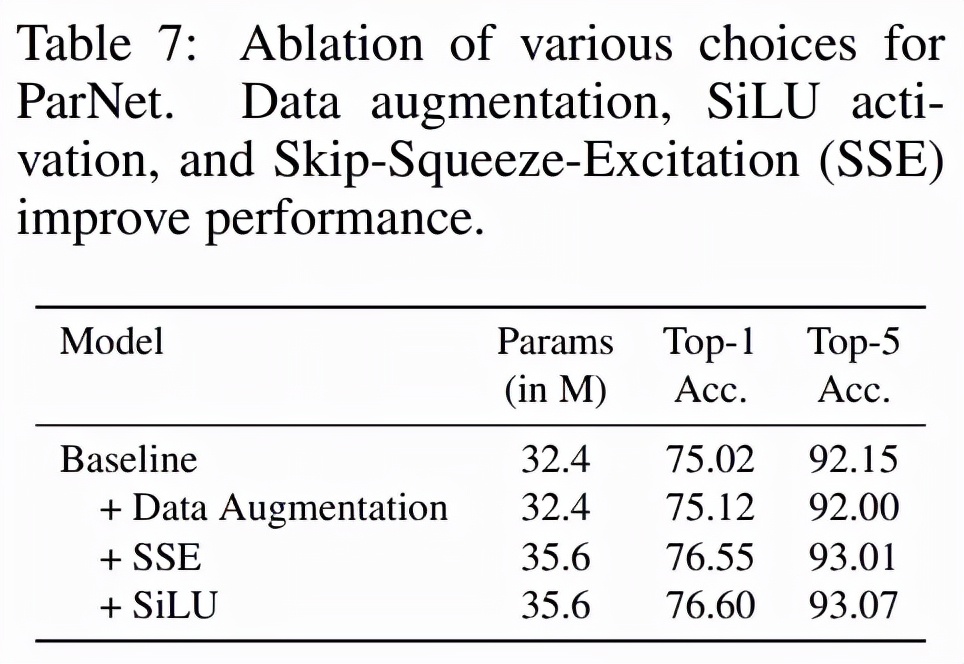

為了測試是否可以簡單地減少 ResNet 的深度并使它們變寬,研究者測試了三個 ResNet 變體:ResNet12-Wide、ResNet14-Wide-BN 和 ResNet12-Wide-SSE。ResNet12-Wide 使用 ResNet 基礎 block,深度為 12,而 ResNet14-Wide-BN 使用 ResNet 瓶頸 block,深度為 14。表 7 展示了對網絡架構和訓練協議的各種設計的消融研究結果,其中包括使用數據增強、SSE block 和 SiLU 激活函數的 3 種情況。

在表 10 中,研究者評估了參數總數相同但分支數不同( 1、2、3、4)的網絡。實驗表明,對于固定數量的參數,具有 3 個分支的網絡具有最高的準確率,并且在網絡分辨率分別為 224x224 和 320x320 這兩種情況下都是最優的。

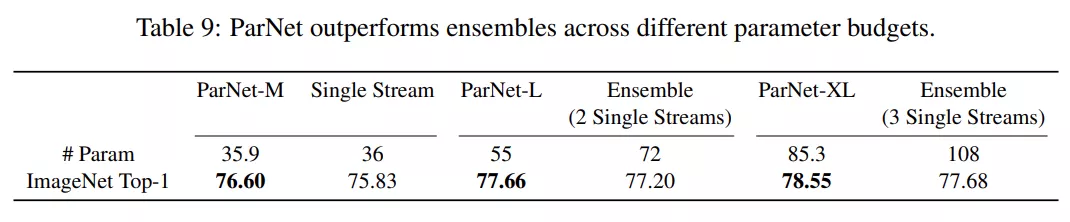

另一種網絡并行化的方法是創建由多個網絡組成的集合體。因此,該研究將 ParNet 和集成的網絡進行對比。如下表 9 所示,當使用較少的參數時,ParNet 的性能優于集成的網絡。