對(duì)比GPU,使用FPGA創(chuàng)建神經(jīng)網(wǎng)絡(luò)

當(dāng)代的CPU按照一維方式進(jìn)行計(jì)算,順序執(zhí)行指令,并將算法分解為逐條加載和執(zhí)行的指令。然而,未來(lái)的計(jì)算發(fā)展趨勢(shì)表明,我們將越來(lái)越多地依賴硬件加速器來(lái)支持并行執(zhí)行,這將成為計(jì)算的常態(tài)。這種發(fā)展趨勢(shì)將統(tǒng)一算法和硬件結(jié)構(gòu)的利用,從而實(shí)現(xiàn)更快、更高效的解決方案。

在這個(gè)發(fā)展趨勢(shì)中,支持二維計(jì)算的GPU的崛起已經(jīng)部分實(shí)現(xiàn)了這一趨勢(shì)。GPU具備大規(guī)模并行計(jì)算的能力,使得許多原本難以并行化的應(yīng)用程序性能得到大幅提升。

圖片

圖片

【左圖】GPU最適合尷尬地并行處理圖像處理算法。視頻畫(huà)面流暢。【右圖】CPU的串行限制導(dǎo)致明顯的延遲和性能不佳。

然而,GPU只能在特定情況下加速特定的算法。未來(lái),通過(guò)互連的CPU和各種硬件加速器實(shí)現(xiàn)超優(yōu)化將成為可能。FPGA將成為這個(gè)未來(lái)的重要組成部分,F(xiàn)PGA允許通過(guò)對(duì)硬件結(jié)構(gòu)進(jìn)行編程來(lái)實(shí)現(xiàn)極度定制化的二維計(jì)算。

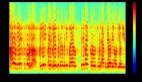

圖片

圖片

【左圖】展示了CPU如何通過(guò)串行執(zhí)行逐個(gè)指令來(lái)解決問(wèn)題的過(guò)程。【右圖】展示了GPU、FPGA和ASIC等硬件加速器如何在空間和時(shí)間上進(jìn)行二維計(jì)算。

本文為大家展示如何將一個(gè)具體的神經(jīng)網(wǎng)絡(luò)用于睡眠追蹤,并將其映射到FPGA上。更重要的是演示將硬件映射到算法所需的關(guān)鍵工具,介紹如何實(shí)現(xiàn)異構(gòu)計(jì)算。

1 睡眠追蹤:鉛筆尖上的神經(jīng)網(wǎng)絡(luò)

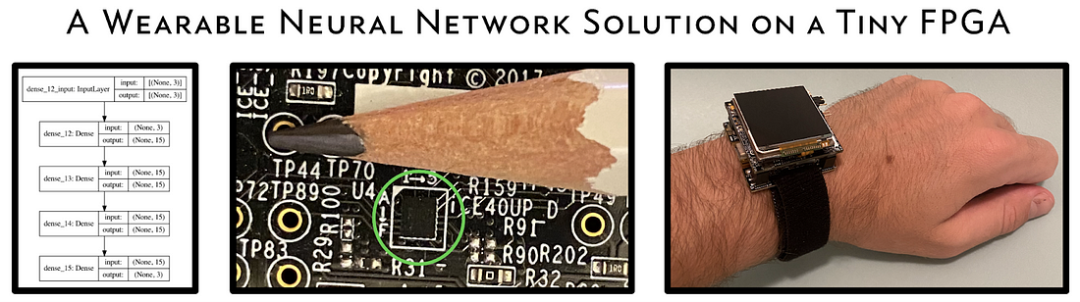

這里制作了一個(gè)基于可穿戴FPGA的睡眠追蹤器。在這個(gè)過(guò)程中,建立了一個(gè)流水線,能夠?qū)⒆畛跤肞ython(Keras)描述的神經(jīng)網(wǎng)絡(luò)映射到硅芯片(FPGA)上。從數(shù)據(jù)采集到神經(jīng)網(wǎng)絡(luò)預(yù)測(cè),整個(gè)睡眠追蹤過(guò)程完全在一個(gè)微小的FPGA上運(yùn)行,沒(méi)有處理器參與。

圖片

圖片

在比鉛筆尖還小的FPGA上部署了三層前饋神經(jīng)網(wǎng)絡(luò)(左圖),這些FPGA可以在iCE40 Ultra Wearable Development Platform(右圖中綠色圈出)中找到。

利用密歇根大學(xué)(Walch等人,2019年的《睡眠》期刊)開(kāi)發(fā)的經(jīng)過(guò)同行評(píng)審的算法實(shí)現(xiàn)。這是首個(gè)開(kāi)源的睡眠數(shù)據(jù)集和相應(yīng)的算法存儲(chǔ)庫(kù)。

使用來(lái)自該項(xiàng)目的有標(biāo)簽數(shù)據(jù)對(duì)這里的FPGA神經(jīng)網(wǎng)絡(luò)(NN)核心進(jìn)行了驗(yàn)證。使用的神經(jīng)網(wǎng)絡(luò)是一個(gè)多層感知器,以加速度計(jì)數(shù)據(jù)、心率和晝夜節(jié)律數(shù)據(jù)作為輸入,并以91.3%的整體準(zhǔn)確率預(yù)測(cè)清醒、快速動(dòng)眼(REM)睡眠和非快速動(dòng)眼(non-REM)睡眠。

圖片

圖片

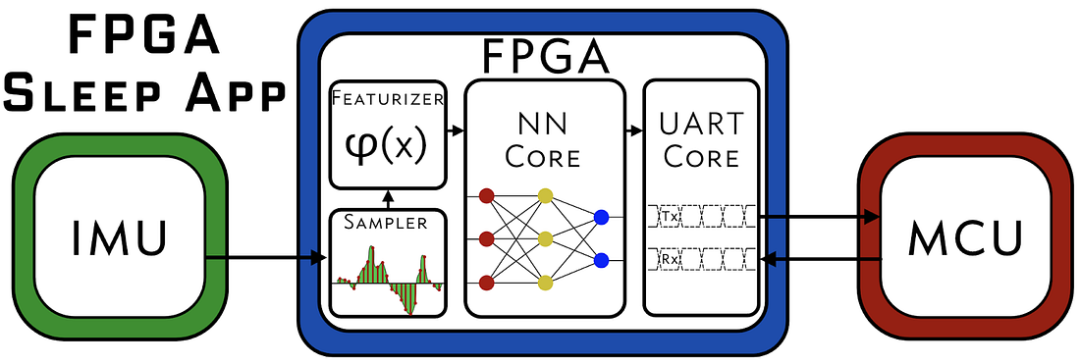

FPGA睡眠追蹤器的高級(jí)架構(gòu)圖。在前端,STM IMU芯片是連接到FPGA的數(shù)據(jù)源。在后端,可以連接一個(gè)主機(jī)計(jì)算機(jī)來(lái)讀取數(shù)據(jù)并向睡眠追蹤器發(fā)送命令。從頭開(kāi)始使用SystemVerilog自己開(kāi)發(fā)了采樣器、特征提取器、NN核心和UART核心。這能夠?qū)崿F(xiàn)一個(gè)在微小FPGA上可部署的高效解決方案。

構(gòu)建的參數(shù)化定義的FPGA NN核心是獨(dú)立于供應(yīng)商的,并且適用于超出此應(yīng)用范圍的其他應(yīng)用,因?yàn)榱魉€允許在一定約束條件下輕松更新模型形狀和參數(shù)。

2 可適應(yīng)加速器上二維算法的未來(lái)

如今,部署可適應(yīng)加速器(如FPGA)是一項(xiàng)高摩擦且耗時(shí)的任務(wù)。將從今天的實(shí)踐和未來(lái)的改進(jìn)角度描述FPGA開(kāi)發(fā)的三個(gè)方面。

2.1 二維算法將以高級(jí)方式(例如Python)進(jìn)行描述并自動(dòng)部署

編寫(xiě)FPGA代碼是一項(xiàng)神秘的任務(wù),需要不同于數(shù)據(jù)科學(xué)家和大多數(shù)軟件工程師的專業(yè)知識(shí)。對(duì)于本來(lái)可以極大受益于基于FPGA的二維加速的團(tuán)隊(duì)來(lái)說(shuō),這可能成為一道阻礙。能夠使用熟悉的高級(jí)語(yǔ)言(如Python)描述針對(duì)FPGA的算法對(duì)于普及FPGA的使用至關(guān)重要。FPGA專家也將從這種基礎(chǔ)設(shè)施帶來(lái)的主要效率提升中受益。

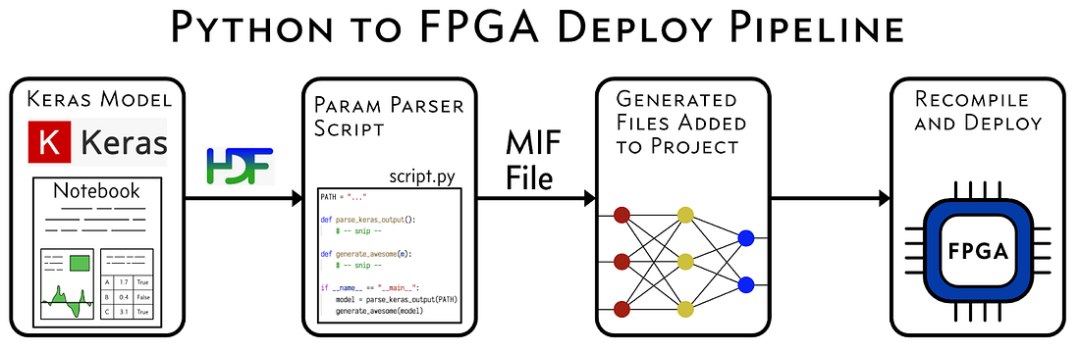

要在應(yīng)用中部署一個(gè)新的睡眠追蹤器網(wǎng)絡(luò),用戶只需運(yùn)行一個(gè)腳本并輕微修改幾個(gè)文件。無(wú)需具備硬件知識(shí),也無(wú)需編寫(xiě)新的SystemVerilog代碼。

圖片

圖片

神經(jīng)網(wǎng)絡(luò)部署流程使非FPGA專家能夠訓(xùn)練新模型并部署到FPGA上。流程的步驟包括訓(xùn)練和導(dǎo)出Keras模型,使用腳本將輸出模型解析為FPGA編譯器工具鏈所需的數(shù)據(jù),更新頂層FPGA項(xiàng)目文件中的模型常量,然后重新編譯FPGA比特流。

這有效的原因在于只允許使用高度約束的模型。未來(lái),更通用的高級(jí)綜合(HLS)工具,如賽靈思(Xilinx)的Vitis HLS和谷歌的XLS,將允許用戶提供要部署到可適應(yīng)加速器的通用高級(jí)算法描述。

2.2 將以Python等語(yǔ)言高效地測(cè)試和調(diào)試二維算法

仿真、驗(yàn)證和調(diào)試是FPGA應(yīng)用設(shè)計(jì)過(guò)程中關(guān)鍵的部分。這些過(guò)程也將從高級(jí)接口和工具中得到重大改進(jìn)。

圖片

圖片

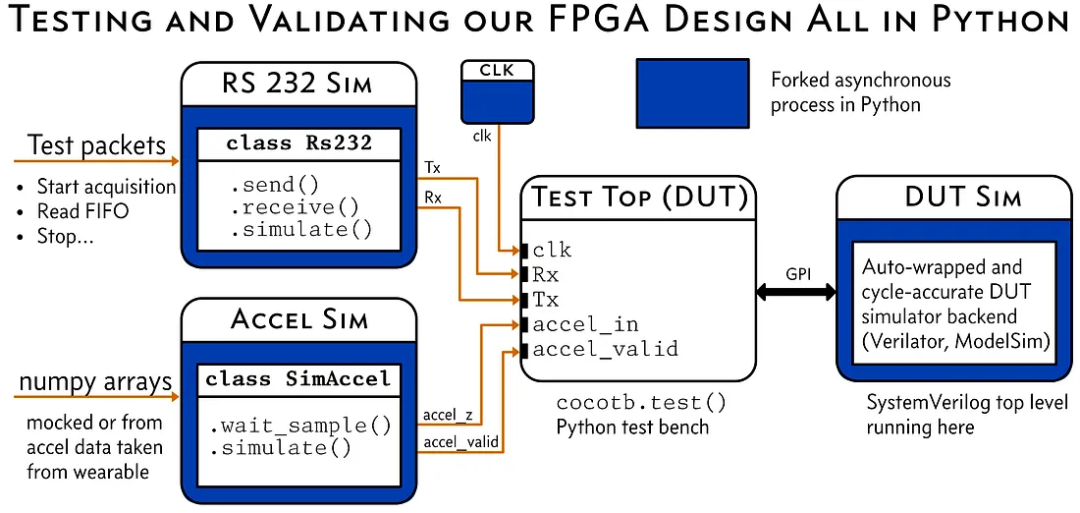

睡眠追蹤器應(yīng)用的頂層測(cè)試平臺(tái)圖。能夠使用Cocotb和Python進(jìn)行測(cè)試、驗(yàn)證和調(diào)試FPGA設(shè)計(jì),這是一大福音。Python的異步/等待語(yǔ)法的便利性以及在Python中輕松模擬子組件/導(dǎo)入測(cè)試數(shù)據(jù)的簡(jiǎn)易性極大地加快了我們的工作。

已經(jīng)取得了巨大的進(jìn)展。例如,雖然直接在SystemVerilog中編寫(xiě)了所有組件,但在所有的離設(shè)備驗(yàn)證和測(cè)試平臺(tái)(對(duì)每個(gè)模塊和整個(gè)睡眠應(yīng)用)上都使用了Cocotb,而從未離開(kāi)過(guò)Python。借助Cocotb,可以在Python生態(tài)系統(tǒng)中使用周期精確的仿真,這對(duì)于FPGA驗(yàn)證非常重要,而且對(duì)開(kāi)發(fā)人員非常高效。

2.3 Rust將成為連接異構(gòu)系統(tǒng)的粘合劑

嵌入式工程師常見(jiàn)的情況是在硬件加速器(如FPGA)和主機(jī)CPU之間建立通信。這項(xiàng)工作因其繁瑣和容易出錯(cuò)而臭名昭著。

在Rust中構(gòu)建了FPGA睡眠應(yīng)用程序的設(shè)備驅(qū)動(dòng)程序和更高級(jí)的Session API。前者實(shí)現(xiàn)了自定義數(shù)據(jù)包協(xié)議,而使用后者創(chuàng)建了各種與FPGA睡眠應(yīng)用程序交互的程序。Rust是一個(gè)很好的解決方案,因?yàn)槠漕愋拖到y(tǒng)和靜態(tài)檢查使得編寫(xiě)安全的低級(jí)代碼和符合人體工程學(xué)的高級(jí)API變得更加容易。本演講的后半部分將詳細(xì)介紹其中一些特性。

相信Rust是將異構(gòu)計(jì)算系統(tǒng)連接在一起的最佳選擇。在這個(gè)角色中,Rust將提供低級(jí)通信的安全性,減少驅(qū)動(dòng)程序的脆弱性,并為算法之間跨硬件邊界進(jìn)行通信提供人體工程學(xué)的API。

圖片

圖片

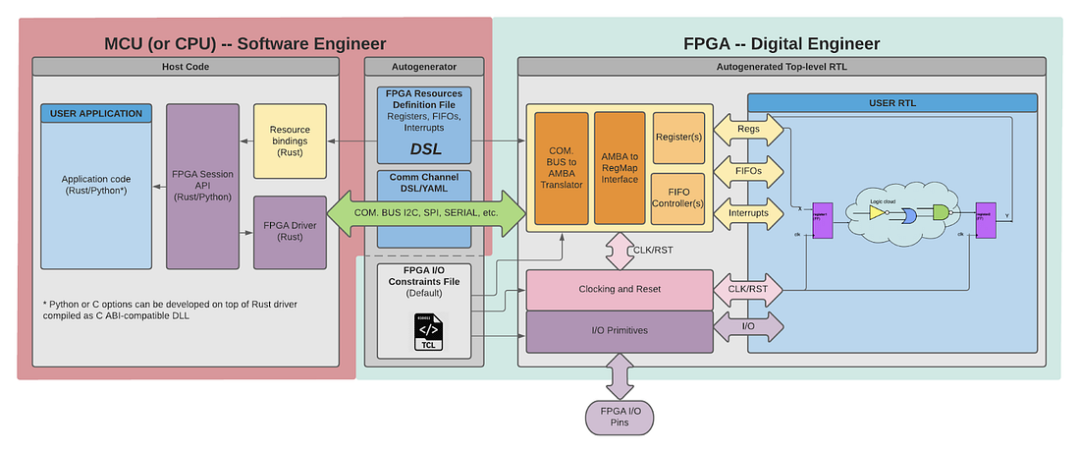

將Rust作為CPU <-> FPGA的粘合劑的展望,包括針對(duì)常見(jiàn)I/O類的代碼生成設(shè)施。