新興的硬件安全技術

1.介紹

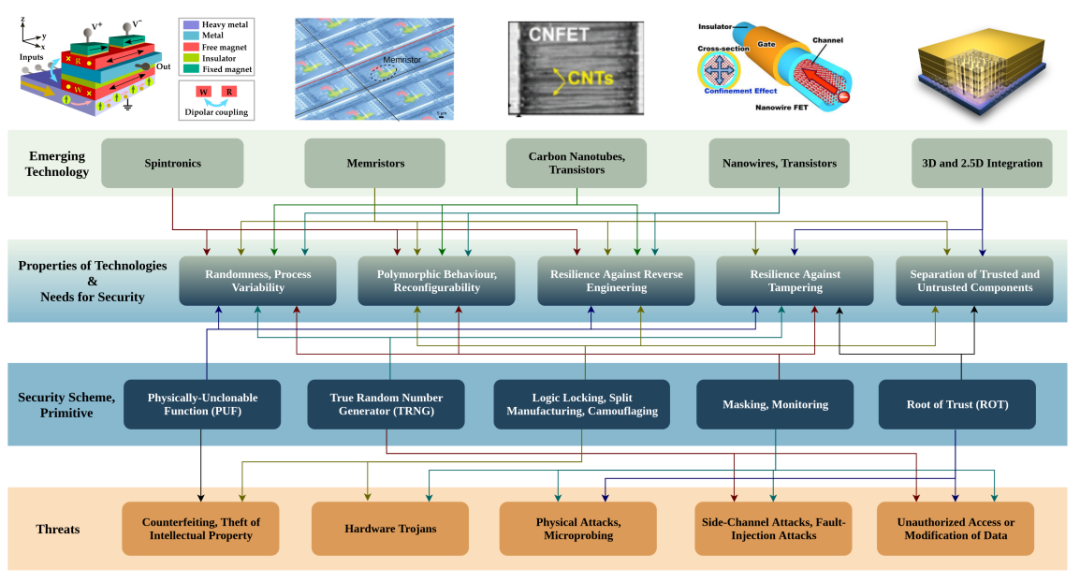

圖1展現(xiàn)了本文所涉及的新興硬件安全技術、以及新興硬件安全技術中與硬件安全相關的和有利于硬件安全的特性、相應的安全方案以及這些方案所應對的安全威脅。

圖片

圖片

2.新興器件

新興器件有一些共同的有趣特性,這些特性是傳統(tǒng)CMOS技術難以實現(xiàn)的。更具體地說,自旋電子學、憶電阻器、碳納米管晶體管和NWFET都可以定制,以包含顯著的可變性、隨機性、可重構性、多態(tài)行為、反逆向工程的彈性,也可能用于分離可信和不可信部件(后者通過分裂制造的方式)。因此,這些器件可以很好地服務于puf、trng、IP保護方案,并屏蔽側通道泄漏。此外,憶阻器還可以通過破壞性數(shù)據(jù)管理提供抗篡改的彈性。

這種基于新興器件的安全方案的實際實施前景取決于各個方面,從一般的電路設計和安全分析,到制造能力和設備成熟度等等。其他論文也回顧了硬件安全背景下的新興器件,例如,詳見[1-3]。

2.1 自旋電子學

當前各種研究都提出了IP保護的多態(tài)行為和/或可重構性。例如,Alasad 等人[4]使用全自旋邏輯進行偽裝。然而,他們提出了一些設備獨特的原語布局;在基于圖像的逆向工程中很容易區(qū)分出來。此外,它們的原語能量消耗相對較高,ns-range延遲大約消耗350uw。在[5]中,作者介紹了針對設計混亂引入了基于自旋電子學的可重構查找表(lut)。然而,這些方法在抗SAT攻擊方面可能達不到預期的效果。還要注意,這種方法在概念上類似于利用傳統(tǒng)的現(xiàn)場可編程門陣列的設計混淆。在[7]和[6,8]中,分別基于疇壁運動器件和在巨自旋霍爾效應(GSHE)器件研究了多態(tài)和模糊邏輯。后一種邏輯研究相對于前一種研究的重要好處是它們的每臺設備支持所有16種可能的功能;這使得這些設備在SAT彈性方面優(yōu)于其他設備。

在[9]中,提出了基于多態(tài)電磁自旋軌道(MESO)器件的“動態(tài)偽裝”的概念。與常規(guī)的偽裝不同,這種概念也能針對制造廠和測試設施中的“對手”從而起到保護作用,因為真正的功能只在稍后的多態(tài)織物中配置。因此,“動態(tài)偽裝”在概念上也類似于邏輯鎖定。然而,與鎖定不同的是,實現(xiàn)這種安全性不需要額外的設備或門。

人們注意到自旋電子學可以提供一些抵御側信道攻擊的彈性。例如,這些器件的磁電開關不發(fā)射光子;首先可以排除中的相關的攻擊。由于自旋電子學用于邏輯、基于磁場或溫度曲線的故障注入和側信道攻擊可能更難實現(xiàn),這與用于記憶的自旋電子學不同。此外,在[10]中,作者使用自旋電子學來構建多態(tài)電路和不同的電路模板,在運行時進行隨機切換,以屏蔽功率側信道。

在[11]中,作者提倡在puf的疇壁存儲器中制造納米線的工藝變化。在[12]中,作者利用了trng中納米磁鐵固有的隨機自旋開關機制。通過器件級模擬,作者證明了他們的TRNG器件可以在很大的溫度范圍內(nèi)工作,不受工藝變化的影響,并且可以以比CMOS TRNG顯著更小的布局成本實現(xiàn)。在[13]中,作者提出了一種基于反鐵磁的安全內(nèi)存方案,該方案提供了對篡改、側通道和讀出攻擊的保護,并保證了比STT-RAM或pcm更低的位能量。

大多數(shù)研究都集中在電路設計和安全性分析上,而對技術方面的研究很少。盡管自旋電子學在應用方面取得了快速進展,但在相關安全研究中考慮技術探索似乎也很重要。

2.2 記憶電阻器

在硬件安全方案中使用憶阻器的潛力在幾年前就已被認識到,例如在2013年利用憶阻器的過程變化和隨機操作的puf。最近,另一個PUF概念被提出,該概念利用憶阻器的非線性I-V特性(“捏滯”),并應用憶阻電導的模擬調(diào)諧,以提高這類PUF的性能和實用性,并降低外圍電路的復雜性。[14]的作者為他們的PUF概念提供了實驗演示和測量結果。

記憶交叉條數(shù)組是密匙安全管理的核心。作者建議將記憶電阻器件的唯一指紋與這些器件內(nèi)的鍵值存儲相結合。他們構建了控制電路,一旦提取指紋(用于驗證芯片的真實性),密鑰就會被銷毀。因此,秘密密鑰在芯片上保持“活性”,以啟用其功能(遵循邏輯鎖定的概念),直到執(zhí)行任何讀取。作者為他們的概念提供了實驗證明和測量結果。這樣的概念對于邏輯鎖定的實用性來說是重要的一步,它需要防篡改存儲器來保證它的安全,以對抗領域中的惡意終端用戶。

在[15]中,作者還在憶阻器的背景下提出了用于混淆的多態(tài)電路。這是可能的,因為在原則上,在這種模糊邏輯中的憶阻器件的功能可以重新配置。雖然作者提供了電路和布局級別的第一個研究——盡管沒有技術探索和庫描述的細節(jié)——他們沒有提供任何實驗演示。此外,其他研究對基于憶阻的邏輯的延遲和功耗提出了警告,除非對電路結構進行優(yōu)化,這似乎與混淆原理相沖突。

2.3 碳納米管和碳納米管場效應晶體管

在[16]中,作者提出了利用碳納米管制造可變性的puf以及洛倫茲混沌系統(tǒng)的概念。后者的作用是增強puf的輸入和輸出的去相關性,從而使它們更能抵御機器學習攻擊。在[17]中,作者對cntfet進行了基于仿真的關于木馬檢測、電源側通道泄漏和偽裝的研究,發(fā)現(xiàn)與傳統(tǒng)CMOS技術相比,cntfet在各方面都更有前途。在[2]中,作者綜述了CNTS在puf、trng中的應用,并提出該技術可用于檢測微探針或其他侵入性攻擊的新型傳感器。

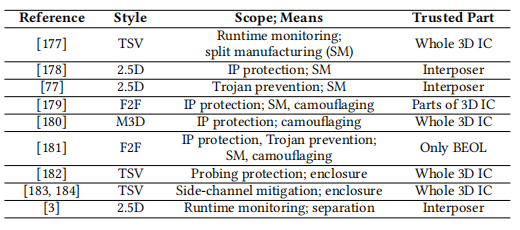

表1:利用2.5D/3D集成提高硬件安全性的精選作品

圖片

圖片

2.4 碳納米管和納米線場效應晶體管

在[18]中,作者提出了用于偽裝的硅納米線場效應晶體管。更具體地說,它們利用nwfet中可控的雙極性來建立一個包含NAND、NOR、XOR和XNOR功能的偽裝原語。作者還建立了一個多態(tài)NAND/NOR門,并給出了電路仿真結果。然而,在[6]中,研究表明這些原語容易受到SAT攻擊。

在[19]中,作者首先探討了如何利用晶體管級可重構性在硅納米場效應晶體管模型的背景下進行邏輯鎖定和分裂制造。其次,他們研究了如何利用可重構性來誘導短路電流或開路配置,從本質(zhì)上消除芯片的可靠性和功能特性;作者認為,可重構nwfet的這一關鍵特性可能被惡意利用為以可靠性為中心的木馬,也可能被故意利用為“殺死開關”。在[20]中,利用納米線與等離子子相互作用的光學檢測被提出和實驗證明。這個想法適用于芯片(或其他商品)的標簽和認證。由于不需要納米線,作者在中提出了等離子體增強光puf的概念,并提供了物理模擬結果和安全性分析。

3. 3D和2.5D集成

3D和2.5D集成為提高硬件安全性提供的主要好處是:組件的物理分離,無論是跨互連、有源設備,還是兩者都有;組件的物理外殼,以保護它們免受現(xiàn)場對抗活動的影響。其他論文也回顧了3D和2.5D集成對硬件安全的好處和壞處,例如,詳見[21]。

3.1 硬件的機密性和完整性:邏輯鎖定

3D和2.5D集成還沒有被用于邏輯鎖定。在松散相關的工作中,利用鎖定原則來推進分離制造的概念。更具體地說,它們鎖定FEOL并將解鎖工作委托給一個獨立的、受信任的BEOL設施。作者指出,他們的方案也可以在包或板級別解鎖,這很可能建議作為2.5D IC實現(xiàn)。

3.2 硬件的機密性和完整性:偽裝

第一個專門為3D集成提出偽裝的人,是針對M3D IC。作者開發(fā)并描述了自定義M3D偽裝庫,并在門級和芯片級評估了他們的方案。

這種偽裝是通過虛擬接觸來實現(xiàn)的,在經(jīng)典二維集成電路中這種方法已經(jīng)被提出。因此,雖然在概念上并不新鮮,但[22]中的工作利用了M3D集成電路提供的好處,以努力提高偽裝的可伸縮性。這是值得注意的,因為現(xiàn)有技術的偽裝可能會產(chǎn)生相當大的布局成本。實際上,這樣的成本只考慮到少數(shù)被偽裝的大門;而有限的偽裝尺度又使此類方案容易受到SAT攻擊。相比之下,[22]報告的工作與常規(guī)2D門相比,平均只消耗25%的電力,15%的延遲成本,43%的面積節(jié)省。

3.3 硬件的機密性和完整性:分裂制造

通過3D和2.5D集成來推進分裂制造似乎既簡單又有前景。這是因為3D和2.5D集成允許將設計分成多個芯片,這些芯片可以獨立維護它們的FEOL和BEOL層,而整個2.5D/3D堆棧可以包含系統(tǒng)級互連的進一步部分。此外,盡管進行了驗證研究,但對經(jīng)典分裂制造的實用性的擔憂仍很普遍,因為單個芯片不必被分裂制造,而只需要整個系統(tǒng)。

2008年,Tezzaron Semiconductor公司概述了這種“3D拆分制造”的概念。各種各樣的研究也在暗示3D拆分制造,但大多數(shù)都有一些局限性。例如,研究[23]僅停留在概念層面,而研究[24]利用2.5D集成,“僅”連接被不可信的設施隱藏。后者基本上等同于傳統(tǒng)的分體式制造,但似乎更實用;盡管如此,研究[24]報告了相當大的布局成本。后來,促進了“原生3D拆分制造”,即在受信任和不受信任的設施之間進行邏輯拆分。

這些后來的研究的一個重要發(fā)現(xiàn)是,3D劃分和垂直互連結構都發(fā)揮著重要作用,并定義了如下的成本——安全權衡:設計被分割到多個芯片上的越多,布局成本就越高,因為需要更多的垂直互連鏈路和相關電路,但卻更靈活和更容易跨3D堆棧“分解”IP。

注意提出了與偽裝相結合的3D分割制造。雖然研究[25]應用了常規(guī)的中心偽裝,但研究[26]認為另一種偽裝方法更適合3D分裂制造,即混淆垂直互連。

其他研究也建議在系統(tǒng)層面進行偽裝。例如,[27]提出通過在“夾在”常規(guī)芯片之間的專用片上網(wǎng)絡(NoC)芯片內(nèi)重路由,來模糊3D IC的垂直互連結構。這個想法在概念上類似于[26]中的隨機路由的概念,但更靈活,但也更昂貴。

3.4 硬件的機密性和完整性:木馬防御

在[26]中,作者利用3D拆分制造提供的好處,推進正式安全但高成本的方案,以減少制造時的木馬插入。

此外,在設計和制造期間,3D和2.5D IC似乎比2D IC更容易受到木馬插入的攻擊。例如,[27]中的研究認為負偏置溫度不穩(wěn)定性(NBTI)效應是隱蔽的特洛伊觸發(fā)器,其動機是熱管理是3D IC的一個眾所周知的挑戰(zhàn)。在更普遍的情況下,3D和2.5D集成相關的供應商和參與者的更廣泛的前景可能為攻擊者嵌入木馬提供新的機會。隨著晶圓級芯片級封裝(WLCSP)被廣泛采用,也面臨著這樣的安全風險。這里假設的攻擊是,一些惡意的集成工具可以在目標芯片和包微碰撞之間放置一個薄的木馬芯片,而該木馬芯片將包含tsv,可以通過和進入這些外部連接,隨意訪問所有這些信號。為了避免視覺或x射線檢查的發(fā)現(xiàn),有人認為將這些tsv與微凸點位置對齊可能就足夠了。

然而,在運行時木馬檢測可以從3D和2.5D集成中受益。這是因為相關的安全特性可以使用可信的制造過程單獨實現(xiàn),并在稍后與待監(jiān)控的商品芯片集成/堆疊。

3.5 硬件的保密性和完整性:puf

將多個芯片集成到3D/2.5D堆棧中似乎有利于理解puf的概念,因為每個芯片都是獨立的過程變化。因此,可以使用多個獨立的熵源來構建puf。在[28,29]中,提出了兩個這樣的方案,進一步利用tsv的過程變化。雖然這些研究在原則上有希望,但沒有考慮到最先進的機器學習攻擊,他們的實際韌性仍有待證明。

3.6 運行時的數(shù)據(jù)安全:未經(jīng)授權的訪問或修改數(shù)據(jù)

3D和2.5D集成可以實現(xiàn)組件的物理分離,因此可以實現(xiàn)可靠的安全功能,如運行時監(jiān)視器或驗證器。

這些方案的實際實施本身可能成為一個漏洞。例如,內(nèi)省接口,這需要在被監(jiān)控的商品芯片中添加額外的邏輯。很容易看出,一旦這些接口被該商品芯片設計或制造的惡意行為者修改,就會失敗。因此,產(chǎn)生了不受歡迎的依賴關系,可能會完全阻礙該計劃。

例如2.5D信任根,它將不受信任的商品芯片與芯片集成到一個包含安全特性的活動中間體上,并進一步形成芯片與芯片之間系統(tǒng)級通信的主干。因此,商品組件和安全組件之間存在明確的物理分離,避免了任何破壞安全的依賴關系。

3.7 運行時數(shù)據(jù)安全:側通道和故障注入攻擊

總的來說,對于3D和2.5D IC來說,考慮到有源器件的密度更高,電路結構和體系結構更復雜,會導致更嘈雜的側信道攻擊變得更加困難。例如,[30]的作者研究了對3D IC的功率側信道攻擊,他們觀察到來自3D IC內(nèi)不同芯片的功率噪聲分布是疊加的。他們還提出了一種用于加密模塊的電壓電源的隨機交聯(lián)方案,以使對此類模塊的攻擊更加困難。

一些現(xiàn)有技術也研究了明確針對3D集成電路的側信道攻擊。例如,[32]和[31]證明對3D IC的熱側信道攻擊可以分別在運行時和設計時減輕。然而,[32]中的方法似乎不太實際;為了減少通過熱模式的信息泄漏,它利用了額外虛擬活動的動態(tài)生成,這進一步加劇了3D集成電路的熱管理挑戰(zhàn)。相比之下,[31]的作者模擬了tsv和模塊放置對樓層規(guī)劃期間熱分布和熱泄漏的影響,從而在降低峰值溫度的同時減少泄漏。

此外,一些研究利用3D和2.5D集成來倡導安全方案,被認為太昂貴。例如,文獻[33]中的研究利用隨機驅(qū)逐和異構延遲作為緩存架構。作者證明,這種技術在2D IC中會產(chǎn)生很高的性能開銷,但即使在3D IC中也可以實現(xiàn)。

與側信道攻擊一樣,由于3D/2.5D IC的物理封裝,故障注入攻擊可能會變得更加困難。

盡管如此,在[34]中,最近的研究表明,橫向重新排列激光裝置足以使這種故障注入攻擊成為可能,同樣適用于背面保護的2D IC,也可能適用于2.5D和3D IC。然而,如果3D集成電路采用專用的物理設計,例如將tsv密集地放置在芯片邊界處,形成“垂直屏蔽”結構,同時在BEOL中使用常規(guī)的屏蔽和背面保護。

3.8 運行時的數(shù)據(jù)安全:物理讀出和探測攻擊

類似于故障注入攻擊,3D/2.5D集成啟用的物理框的概念可能會阻礙讀取和探測攻擊。在[35]中,作者主張3D IC支持“全方位屏蔽”。類似的防止探測的保護在之前已經(jīng)討論過。

參考文獻

[1] J. Rajendran et al., “Nano meets security: Exploring nanoelectronic devices for security applications,” Proc. IEEE, vol. 103, no. 5, pp. 829–849, 2015. https: //doi.org/10.1109/JPROC.2014.2387353

[2] S. Ghosh, “Spintronics and security: Prospects, vulnerabilities, attack models, and preventions,” Proc. IEEE, vol. 104, no. 10, pp. 1864–1893, 2016. https://doi. org/10.1109/JPROC.2016.2583419

[3] F. Rahman et al., “Security beyond CMOS: Fundamentals, applications, and roadmap,” Trans. VLSI Syst., vol. PP, no. 99, pp. 1–14, 2017. https://doi.org/10. 1109/TVLSI.2017.2742943

[4] Q. Alasad, J. Yuan, and D. Fan, “Leveraging all-spin logic to improve hardware security,” in Proc. Great Lakes Symp. VLSI, 2017, pp. 491–494. https://doi.org/10. 1145/3060403.3060471

[5] T. Winograd et al., “Hybrid STT-CMOS designs for reverse-engineering prevention,” in Proc. Des. Autom. Conf., 2016, pp. 88–93. https://doi.org/10.1145/ 2897937.2898099

[6] S. Patnaik et al., “Spin-orbit torque devices for hardware security: From deterministic to probabilistic regime,” Trans. Comp.-Aided Des. Integ. Circ. Sys., vol. 39, pp. 1591–1606, 2019. https://doi.org/10.1109/TCAD.2019.2917856

[7] F. Parveen, Z. He, S. Angizi, and D. Fan, “Hybrid polymorphic logic gate with 5-terminal magnetic domain wall motion device,” in Proc. Comp. Soc. Symp. VLSI, 2017, pp. 152–157. https://doi.org/10.1109/ISVLSI.2017.35

[8] S. Patnaik et al., “Advancing hardware security using polymorphic and stochastic spin-hall effect devices,” in Proc. Des. Autom. Test Europe, 2018, pp. 97–102. https://doi.org/10.23919/DATE.2018.8341986

[9] N. Rangarajan et al., “Opening the doors to dynamic camouflaging: Harnessing the power of polymorphic devices,” Trans. Emerg. Top. Comp., vol. Early Access, 2020. https://doi.org/10.1109/TETC.2020.2991134

[10] A. Roohi and R. F. DeMara, “PARC: A novel design methodology for power analysis resilient circuits using spintronics,” Trans. Nanotech., vol. 18, pp. 885– 889, 2019. https://doi.org/10.1109/TNANO.2019.2934887

[11] A. S. Iyengar, S. Ghosh, and K. Ramclam, “Domain wall magnets for embedded memory and hardware security,” J. Emerg. Sel. Topics Circ. Sys., vol. 5, no. 1, pp. 40–50, 2015. https://doi.org/10.1109/JETCAS.2015.2398232

[12] N. Rangarajan, A. Parthasarathy, and S. Rakheja, “A spin-based true random number generator exploiting the stochastic precessional switching of nanomagnets,” J. Appl. Phys., vol. 121, no. 22, p. 223905, 2017. https://doi.org/10.1063/1.4985702

[13] N. Rangarajan et al., “SMART: A secure magnetoelectric antiferromagnet-based tamper-proof non-volatile memory,” vol. 8, pp. 76 130–76 142, 2020. https://doi. org/10.1109/ACCESS.2020.2988889

[14] H. Nili et al., “Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors,” Nature Electronics, vol. 1, no. 3, pp. 197–202, 2018. https://doi.org/10.1038/s41928-018-0039-7

[15] A. Rezaei, J. Gu, and H. Zhou, “Hybrid memristor-CMOS obfuscation against untrusted foundries,” in Proc. Comp. Soc. Symp. VLSI, 2019, pp. 535–540. https: //doi.org/10.1109/ISVLSI.2019.00102

[16] L. Liu, H. Huang, and S. Hu, “Lorenz chaotic system-based carbon nanotube physical unclonable functions,” Trans. Comp.-Aided Des. Integ. Circ. Sys., vol. 37, no. 7, pp. 1408–1421, 2018. https://doi.org/10.1109/TCAD.2017.2762919

[17] C. K. H. Suresh, B. Mazumdar, S. S. Ali, and O. Sinanoglu, “A comparative security analysis of current and emerging technologies,” Micro, vol. 36, no. 5, pp. 50–61, 2016. https://doi.org/10.1109/MM.2016.87

[18] Y. Bi et al., “Emerging technology-based design of primitives for hardware security,” J. Emerg. Tech. Comp. Sys., vol. 13, no. 1, pp. 3:1–3:19, 2016. https: //doi.org/10.1145/2816818

[19] S. Rai et al., “Security promises and vulnerabilities in emerging reconfigurable nanotechnology-based circuits,” Trans. Emerg. Top. Comp., vol. Early Access, 2020. https://doi.org/10.1109/TETC.2020.3039375

[20] Y. Cui et al., “Encoding molecular information in plasmonic nanostructures for anti-counterfeiting applications,” Nanoscale, no. 6, pp. 282–288, 2014. https: //doi.org/10.1039/C3NR04375D

[21] J. Knechtel, S. Patnaik, and O. Sinanoglu, “3D integration: Another dimension toward hardware security,” in Proc. Int. On-Line Test Symp., 2019, pp. 147–150. https://doi.org/10.1109/IOLTS.2019.8854395

[22] C. Yan et al., “Hardware-efficient logic camouflaging for monolithic 3D ICs,” Trans. Circ. Sys., vol. 65, no. 6, pp. 799–803, 2018. https://doi.org/10.1109/TCSII. 2017.2749523

[23] J. Dofe et al., “Security threats and countermeasures in three-dimensional integrated circuits,” in Proc. Great Lakes Symp. VLSI, 2017, pp. 321–326. https: //doi.org/10.1145/3060403.3060500

[24] Y. Xie, C. Bao, and A. Srivastava, “Security-aware 2.5D integrated circuit design flow against hardware IP piracy,” Computer, vol. 50, no. 5, pp. 62–71, 2017. https://doi.org/10.1109/MC.2017.121

[25] P. Gu et al., “Cost-efficient 3D integration to hinder reverse engineering during and after manufacturing,” in Proc. Asian Hardw.-Orient. Sec. Trust Symp., 2018, pp. 74–79. https://doi.org/10.1109/AsianHOST.2018.8607176

[26] S. Patnaik, M. Ashraf, O. Sinanoglu, and J. Knechtel, “A modern approach to IP protection and trojan prevention: Split manufacturing for 3D ICs and obfuscation of vertical interconnects,” Trans. Emerg. Top. Comp., vol. Early Access, 2019. https://doi.org/10.1109/TETC.2019.2933572

[27] J. Dofe, Q. Yu, H. Wang, and E. Salman, “Hardware security threats and potential countermeasures in emerging 3D ICs,” in Proc. Great Lakes Symp. VLSI, 2016, pp. 69–74. https://doi.org/10.1145/2902961.2903014

[28] M. Wang, A. Yates, and I. L. Markov, “SuperPUF: Integrating heterogeneous physically unclonable functions,” in Proc. Int. Conf. Comp.-Aided Des., 2014, pp. 454–461. https://doi.org/10.1109/ICCAD.2014.7001391

[29] C. Wang et al., “TSV-based PUF circuit for 3DIC sensor nodes in IoT applications,” in Proc. Electron. Dev. Solid State Circ., 2015, pp. 313–316. https://doi.org/10.1109/ EDSSC.2015.7285113

[30] J. Dofe and Q. Yu, “Exploiting PDN noise to thwart correlation power analysis attacks in 3D ICs,” in Proc. Int. Worksh. Sys.-Level Interconn. Pred., 2018. https: //doi.org/10.1145/3225209.3225212

[31] J. Knechtel and O. Sinanoglu, “On mitigation of side-channel attacks in 3D ICs: Decorrelating thermal patterns from power and activity,” in Proc. Des. Autom. Conf., 2017, pp. 12:1–12:6. https://doi.org/10.1145/3061639.3062293

[32] P. Gu et al., “Thermal-aware 3D design for side-channel information leakage,” in Proc. Int. Conf. Comp. Des., 2016, pp. 520–527. https://doi.org/10.1109/ICCD. 2016.7753336

[33] C. Bao and A. Srivastava, “3D integration: New opportunities in defense against cache-timing side-channel attacks,” in Proc. Int. Conf. Comp. Des., 2015, pp. 273–280. https://doi.org/10.1109/ICCD.2015.7357114

[34] J. Rodriguez, A. Baldomero, V. Montilla, and J. Mujal, “LLFI: Lateral laser fault injection attack,” in Proc. Worksh. Fault Diag. Tol. Cryptogr., 2019, pp. 41–47. https://doi.org/10.1109/FDTC.2019.00014

[35] J. Knechtel, S. Patnaik, and O. Sinanoglu, “3D integration: Another dimension toward hardware security,” in Proc. Int. On-Line Test Symp., 2019, pp. 147–150. https://doi.org/10.1109/IOLTS.2019.8854395