沖擊6.4GHz!DDR5內(nèi)存首秀,將于2022年普及

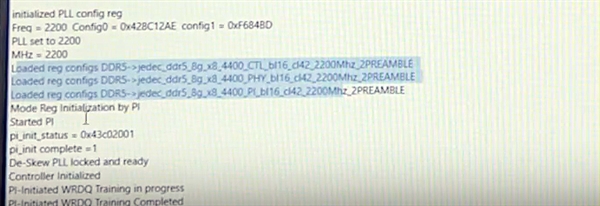

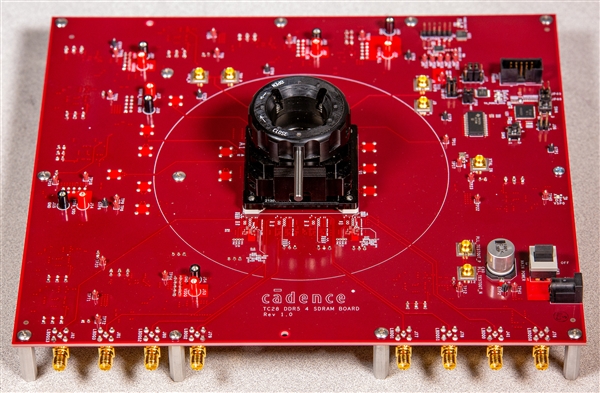

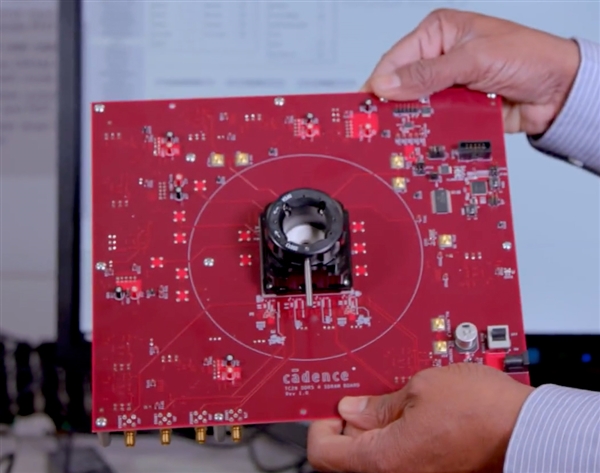

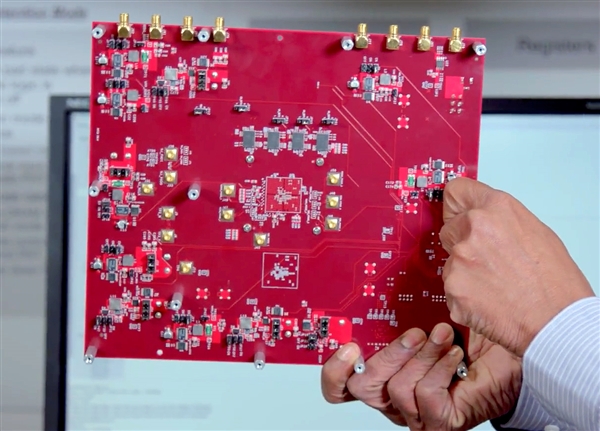

Cadence近日宣布了業(yè)內(nèi)首個(gè)DDR5內(nèi)存的IP接口芯片,包括控制器和PHY物理層,采用臺(tái)積電7nm工藝制造,運(yùn)行頻率達(dá)4400MHz,美光也獻(xiàn)上了自己的DDR5內(nèi)存顆粒。

JEDEC組織目前正在制定DDR5內(nèi)存的標(biāo)準(zhǔn)規(guī)范,預(yù)計(jì)今年夏天完成,所以目前進(jìn)行的還都是一些基礎(chǔ)性研究,DDR5內(nèi)存條到底長什么樣子還得等等。

Cadence DDR5內(nèi)存控制器和物理層的數(shù)據(jù)率為4400MT/s,時(shí)序CL42,搭配美光8Gb DDR5內(nèi)存顆粒原型,電壓僅為1.1V(DDR4 1.2V),波動(dòng)范圍±0.033V。

有了這些基礎(chǔ),SoC芯片廠商就可以開始設(shè)計(jì)并集成DDR5內(nèi)存子系統(tǒng),為未來鋪路。

正如DDR4內(nèi)存頻率從2133MHz一路走到3200MHz(JEDEC標(biāo)準(zhǔn)),4400MHz對于DDR5來說也只是起步,預(yù)計(jì)最終可以達(dá)到6400MHz左右。

除了頻率,DDR5內(nèi)存更看重的其實(shí)是大容量,允許加入內(nèi)部ECC來制造16Gb、32Gb顆粒,單條容量也會(huì)大大提升。

DDR5內(nèi)存仍將沿用288個(gè)針腳的布局,但具體設(shè)計(jì)肯定會(huì)和DDR4有所區(qū)別,并且有兩個(gè)獨(dú)立的32位IO通道,整體架構(gòu)也會(huì)大有不同。

DDR5的其他改進(jìn)還會(huì)有:更好的通道利用率、整合電壓調(diào)節(jié)器、高端模組支持電源管理,等等。

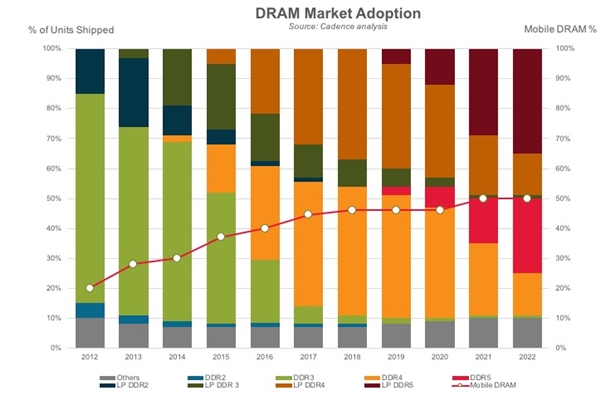

Cadence預(yù)計(jì)第一套DDR5內(nèi)存系統(tǒng)會(huì)在2019年面世,然后迅速普及,2022年就能達(dá)到25%左右的滲透率。